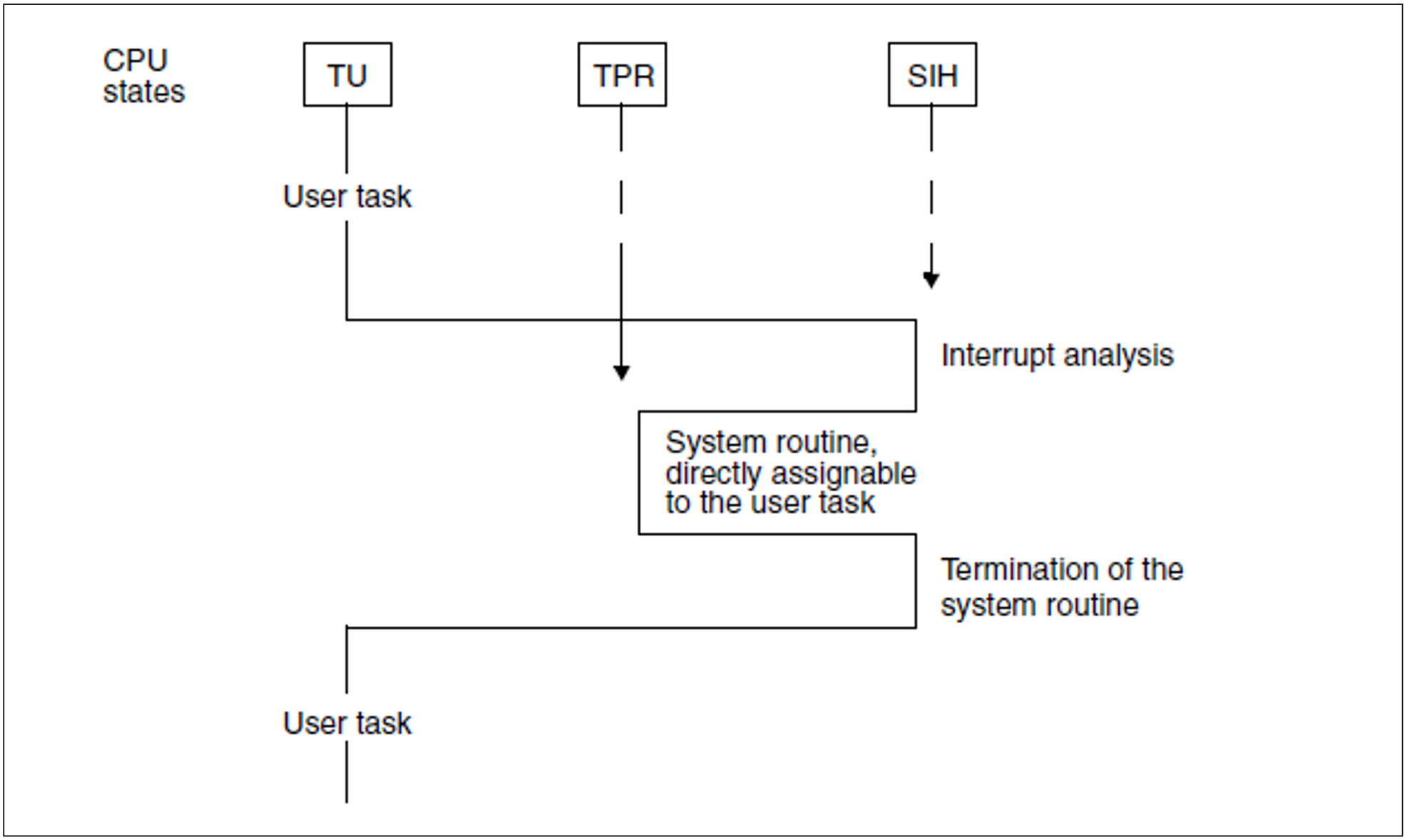

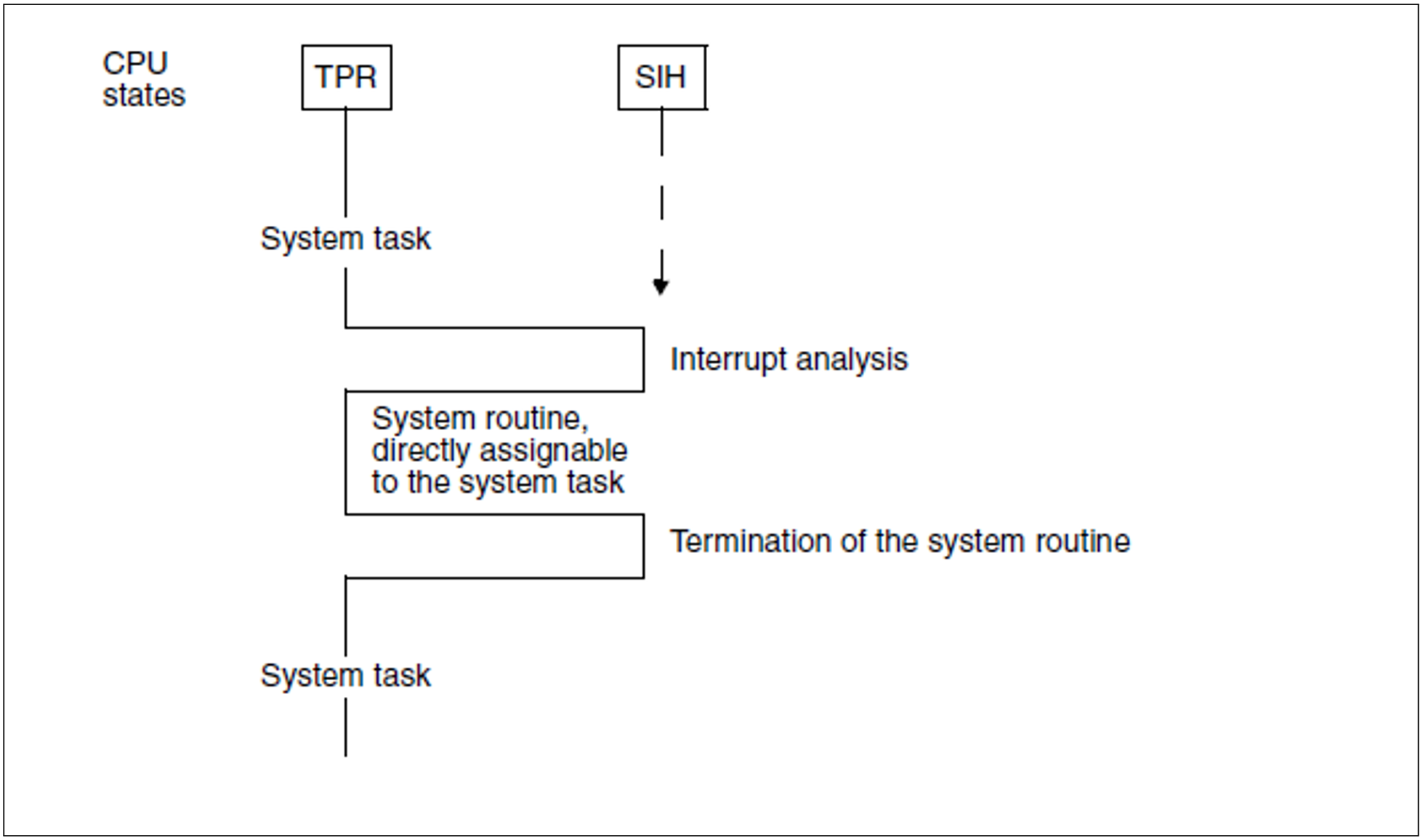

There are four CPU states in BS2000. Of these, the TU, TPR and SIH states are essential to normal operation. The MEH state is used solely to handle hardware errors.

The following definitions apply:

TU: Task Unprivileged

TPR: Task PRivileged

SIH: System Interrupt Handling

MEH: Machine Error Handling

The user task (application program) runs in CPU state TU.

System routines which may be assigned directly to the user task (e.g. SVC: RDATA) are processed in CPU state TPR (see figure 5).

CPU time taken up in the TU and TPR CPU states should be regarded as productive time from the user's standpoint.

The basic control mechanisms of BS2000 are run in CPU state SIH. The SIH CPU state cannot be interrupted except after MEH.

System tasks provide support for organizational tasks; they run in CPU state TPR (see figure 6).

Figure 5: BS2000 CPU states (user task)

Figure 6: BS2000 CPU states (system task)

An interrupt is caused either by a user/system task which requires the support of the operating system or by an event which must be handled by the operating system.

There are five types of interrupt:

SVC interrupt (= task-related interrupt)

A user or system task requests certain system services. The calling task is charged not only for the time for the system routine, but also for the interrupt analysis and the termination of the system routine.

Program interrupt (=task-related interrupt)

This includes “genuine” errors (address error, data error, etc.) which cause the program to abort. These errors may be ignored when considering throughput. Also included are the interrupt causes:

page not in memory (event code 4C)

address translation error (event code 48)

In each case it is impossible to continue the program run for the time being since the addressed page is not immediately available.

There are two possibilities in the case of event code 4C (page not in memory):

The page is still in main memory, namely in the “free pool” (read-only queue or read/write queue):

The page, which has not been addressed for some time, has been entered in the “free pool” by paging management. The program can be resumed following a simple page chaining procedure (PAGE RECLAIM). As a result of the global working set strategies, page reclaiming is a very rare occurrence (see section "Activating/deactivating tasks"). In most cases, it is the result of the first access to a page (First Page Access).

The page is not in main memory and must be entered there by means of a paging I/O operation (PAGE READ).

Event code 48 involves a genuine error in address translation, which causes the program to abort.

Timer/external interrupt (= asynchronous interrupt)

A signal from the interval timer or ETC (Elapsed Time Clock).

I/O interrupt (= asynchronous interrupt)

A signal that an event has occurred in connection with input/output. (In most cases, this involves the occurrence of an end condition when performing the I/O operation.)

Hardware error interrupt (= asynchronous interrupt)

A signal that a hardware error has occurred.

Once the interrupt has been treated (with the exception of the SVC interrupt), the dispatcher (selection) routine of the task initiator will select and pass control to the executable user or system task with the highest priority (task in control; see also section "Initiation/deinitiation of tasks").